AMD ha appena pubblicato la patch di abilitazione iniziale per integrare il supporto del processore Zen 5 nella GNU Compiler Collection.

Phoronix rivela che dopo una lunga attesa, AMD ha finalmente deciso di svegliarsi e portare il supporto Zen 5 per il nuovo compilatore GCC, poiché concorrenti come Intel hanno già spinto per portare il supporto per architetture future il cui rilascio è previsto tra anni.

Intel tende a potenziare il supporto del nuovo compilatore con largo anticipo rispetto al lancio del prodotto per tenere conto del fatto che GCC vede solo una versione principale annuale e LLVM/Clang con un ciclo di rilascio di sei mesi. Inoltre, considerando il modo in cui le distribuzioni Linux pianificano il rilascio annuale di GCC da marzo ad aprile, ad esempio, non è fino al rilascio di Ubuntu XX.10 che passano a una nuova versione del compilatore GCC per impostazione predefinita, come l’imminente Ubuntu 24.04 LTS già impostato su GCC. 13. Ciò ha significato un supporto più tempestivo del compilatore Intel per i clienti mentre AMD tendeva a non pubblicare le patch GCC e LLVM/Clang fino a dopo l’annuncio dei prodotti. A volte si sono affidati anche agli ingegneri del compilatore SUSE per elaborare il supporto post-annuncio.

Con i prodotti AMD Zen 5 non ancora annunciati si temeva che GCC 14 potesse non avere alcuna abilitazione per Znver5 ma invece la notizia positiva è proprio questa ovvero una patch per eseguire -march=znver5 iniziale . In particolare vengono rilevate le funzionalità ISA Zen 5:

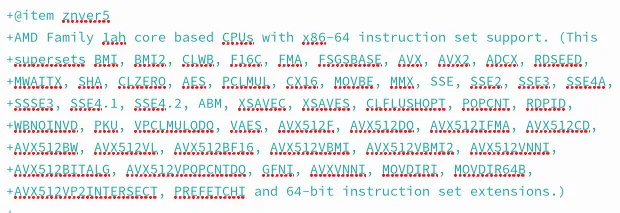

znver5

AMD Family 1ah core based CPUs with x86-64 instruction set support. (This supersets BMI, BMI2, CLWB, F16C, FMA, FSGSBASE, AVX, AVX2, ADCX, RDSEED, MWAITX, SHA, CLZERO, AES, PCLMUL, CX16, MOVBE, MMX, SSE, SSE2, SSE3, SSE4A, SSSE3, SSE4.1, SSE4.2, ABM, XSAVEC, XSAVES, CLFLUSHOPT, POPCNT, RDPID, WBNOINVD, PKU, VPCLMULQDQ, VAES, AVX512F, AVX512DQ, AVX512IFMA, AVX512CD, AVX512BW, AVX512VL, AVX512BF16, AVX512VBMI, AVX512VBMI2, AVX512VNNI, AVX512BITALG, AVX512VPOPCNTDQ, GFNI, AVXVNNI, MOVDIRI, MOVDIR64B, AVX512VP2INTERSECT, PREFETCHI and 64-bit instruction set extensions.)

Rispetto a Zen 4, ciò conferma che AMD Zen 5 aggiunge AVXVNNI, MOVDIRI, MOVDIR64B, AVX512VP2INTERSECT e PREFETCHI.

l’AVX-512 VP2INTERSECT, che è stato trovato dalla parte Intel dai tempi di Tigerlake. MOVDIRI e MOVDIR64B sono stati trovati anche sul lato Intel a partire da Tigerlake. PREFETCHI è entusiasmante e arriva solo dalla parte Intel con Granite Rapids. Infine, AVX-VNNI è una novità per Zen 5 perché è equivalente a AVX512-VNNI con codifica VEX. La patch riafferma che le CPU Zen 5 (Famiglia 1Ah) hanno tutte le stesse funzionalità ISA proprio come ci godiamo con Zen 4 e Zen 4C. Nessuna differenza ISA, per fortuna, né tra server e desktop/mobile.

Vale anche la pena notare dalla patch del compilatore Znver5 che c’è un tubo AGU aggiuntivo (4 in totale) rispetto alla generazione attuale e ora sei tubi ALU rispetto ai quattro tubi ALU con Zen 4.

L’abilitazione iniziale di AMD Zen 5 per GCC è ora sulla mailing list , ma si spera verrà unita a GCC 14 Git a breve. Vale la pena notare che il codice Znver5 per ora riutilizza il modello di pianificazione Znver4 esistente con l’ingegnere AMD che riferisce che il modello aggiornato per Zen 5 verrà aggiunto in seguito.

Al momento della stesura delle patch del compilatore LLVM/Clang per Znver5 devono ancora essere pubblicate, ma presumibilmente presto verrà data la patch GCC Zen 5 ora pubblica e almeno dal lato LLVM si occupano solo del ciclo di rilascio di sei mesi e delle distribuzioni Linux tendendo ad inserire le nuove versioni di LLVM più rapidamente.

0 commenti